A. Senthilkumara, A.M. Natarajanb1 a Professor, Department of ECE, Kongu Engineering College, Perundurai, Erode., TN, India.

b Professor, Department of ECE, Bannari Amman Institute of Technology, Sathy, Erode TN, India.

Download Citation:

|

Download PDF

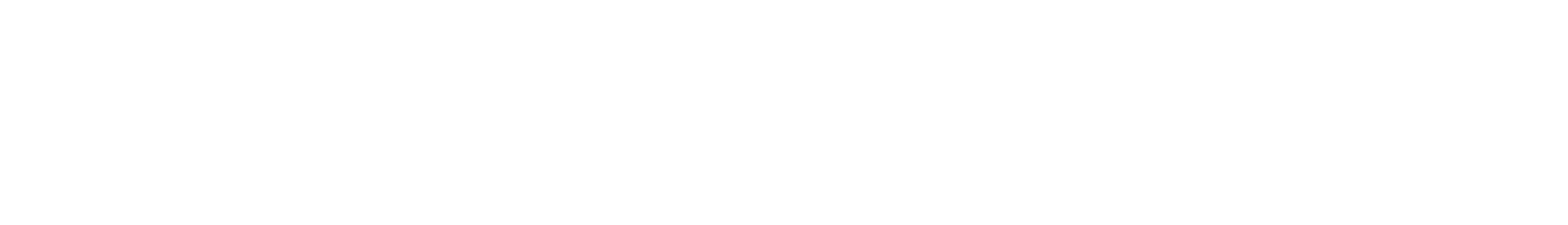

Asynchronous design is progressively becoming more attractive alternative to synchronous design because of its potential for high-speed and low-power. The pipelining technique is very effective for synchronous digital designs. This paper proposes the design of pipelined Finite Impulse Response (FIR) filter using asynchronous quasi-delay-insensitive (QDI) template based on Reduced Slack Pre-Charged Half Buffer (RSPCHB). Both synchronous and asynchronous pipelined FIR filter have been designed using TSMC 0.18-µm CMOS technology. HSPICE simulation shows that the speed of the asynchronous system has been improved 12 times with 2 times increased area over synchronous design.ABSTRACT

Keywords:

Asynchronous; FIR Digital Filter; Pipelining; QDI; Reduced Slack Pre-charged Half Buffer (RSPCHB)

Share this article with your colleagues

REFERENCES

ARTICLE INFORMATION

Accepted:

2008-12-14

Available Online:

2008-11-01

Senthilkumar, A., Natarajan, A.M. 2008. Design of high speed asynchronous pipelined FIR filter using quasi delay insensitive reduced slack Pre-Charged half buffer. International Journal of Applied Science and Engineering, 6, 181–197.https://doi.org/10.6703/IJASE.2008.6(2).181

Cite this article: