Sunny Arief Sudiro1*, Aqwam Rosadi Kardian1, Sarifuddin Madenda2, Lingga Hermanto2 1 STMIK Jakarta STI&K Jl. BRI No. 17 Radio Dalam Kebayoran Baru Jakarta Indonesia

2 Gunadarma University Jl. Margonda Raya No. 100 Depok Jawa Barat Indonesia

Download Citation:

|

Download PDF

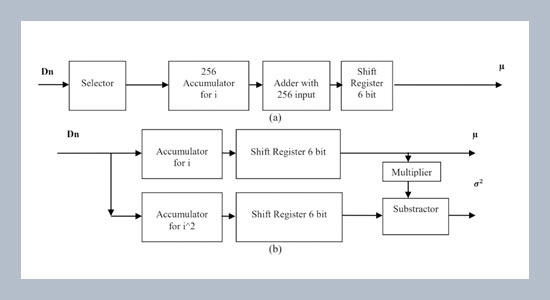

Statistical formula processing an image data is commonly used in image processing. In software processing this formula and accessing data stored in memory is an easy task, but in hardware implementation, it is more difficult task due to many of constraints. This article presents hardware implementation of mean & variance statistic formula in effective and efficient way using FGPA Device. The design of circuit for both formulas proposed in this article need only two additions component (in two accumulators) and two shift-right-registers will be used for divisor circuits, one subtractor and one multiplier. In the experiment, processing an image size 8x8 pixels need 64 clocks cycle to conclude the mean & variance calculations. More than 1024 additions component is needed in some design so this design is more efficient.ABSTRACT

Keywords:

Mean, Variance, FPGA, Accumulator, Counter.

Share this article with your colleagues

REFERENCES

ARTICLE INFORMATION

Received:

2020-06-05

Accepted:

2020-12-31

Available Online:

2021-03-01

Sudiro, S.A., Kardian, A.R., Madenda, S., Hermanto, L. 2021. Mean and variance statistic for image processing on FPGA. International Journal of Applied Science and Engineering, 18, 2020115. https://doi.org/10.6703/IJASE.202103_18(1).009

Cite this article:

Copyright The Author(s). This is an open access article distributed under the terms of the Creative Commons Attribution License (CC BY 4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are cited.